# cādence<sup>®</sup>

## **OrCAD Capture User Guide**

Product Version 16.6 October 2012 Product Version 16.6 October 2012

© 1996–2012 Cadence Design Systems, Inc. All rights reserved. Portions © Apache Software Foundation, Sun Microsystems, Free Software Foundation, Inc., Regents of the University of California, Massachusetts Institute of Technology, University of Florida\_\_\_ Used by permission. Printed in the United States of America.

Cadence Design Systems, Inc. (Cadence), 2655 Seely Ave., San Jose, CA 95134, USA.

OrCAD Capture contains technology licensed from, and copyrighted by: Apache Software Foundation, 1901 Munsey Drive Forest Hill, MD 21050, USA © 2000-2005, Apache Software Foundation. Sun Microsystems, 4150 Network Circle, Santa Clara, CA 95054 USA © 1994-2007, Sun Microsystems, Inc. Free Software Foundation, 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA © 1989, 1991, Free Software Foundation, Inc. Regents of the University of California, Sun Microsystems, Inc., Scriptics Corporation, © 2001, Regents of the University of California. Daniel Stenberg, © 1996 - 2006, Daniel Stenberg. UMFPACK © 2005, Timothy A. Davis, University of Florida, (davis@cise.ulf.edu). Ken Martin, Will Schroeder, Bill Lorensen © 1993-2002, Ken Martin, Will Schroeder, Bill Lorensen. Massachusetts Institute of Technology, 77 Massachusetts Avenue, Cambridge, Massachusetts, USA © 2003, the Board of Trustees of Massachusetts Institute of Technology. vtkQt, © 2000-2005, Matthias Koenig. All rights reserved.)

**Trademarks**: Trademarks and service marks of Cadence Design Systems, Inc. contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 800.862.4522.

Open SystemC, Open SystemC Initiative, OSCI, SystemC, and SystemC Initiative are trademarks or registered trademarks of Open SystemC Initiative, Inc. in the United States and other countries and are used with permission.

All other trademarks are the property of their respective holders.

**Restricted Permission:** This publication is protected by copyright law and international treaties and contains trade secrets and proprietary information owned by Cadence. Unauthorized reproduction or distribution of this publication, or any portion of it, may result in civil and criminal penalties. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. Unless otherwise agreed to by Cadence in writing, this statement grants Cadence customers permission to print one (1) hard copy of this publication subject to the following conditions:

1. The publication may be used only in accordance with a written agreement between Cadence and its customer.

- 2. The publication may not be modified in any way.

- 3. Any authorized copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement.

- 4. The information contained in this document cannot be used in the development of like products or software, whether for internal or external use, and shall not be used for the benefit of any other party, whether or not for consideration.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

## Contents

| 1.                                           | 28 |

|----------------------------------------------|----|

| Before you begin                             | 28 |

| Welcome                                      | 28 |

| How to use this guide                        | 28 |

| Symbols and conventions                      | 28 |

| OrCAD Capture                                | 29 |

| Related documentation                        | 30 |

| 2.                                           | 32 |

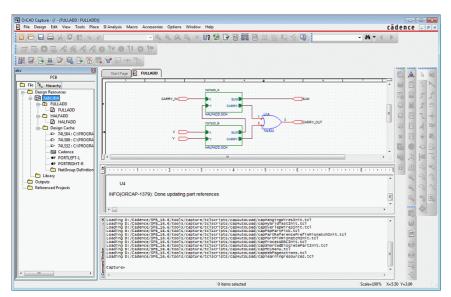

| About the Capture Workspace                  | 32 |

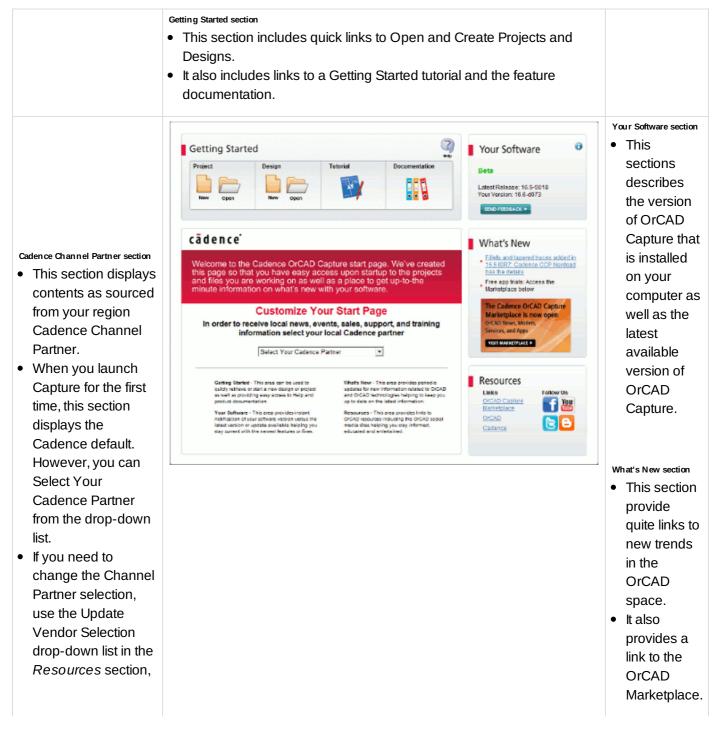

| The Start Page                               | 32 |

| Getting Started section                      | 33 |

| Your Software section                        | 33 |

| Cadence Channel Partner section              | 33 |

| What's New section                           | 33 |

| Resources section                            | 34 |

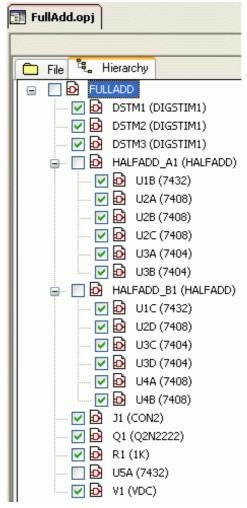

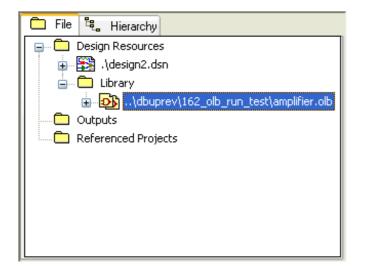

| The Project Manager                          | 34 |

| Views                                        | 35 |

| File view                                    | 35 |

| Hierarchy view                               | 35 |

| Project manager behavior                     | 36 |

| One design for one project                   | 36 |

| The Session Log                              | 36 |

| The TCL Command Window                       | 37 |

| Schematic Page and Part Editors              | 38 |

| Schematic Page Editor                        | 38 |

| Schematic Part Editor                        | 38 |

| Moving around in the editors                 | 39 |

| Scrolling                                    | 39 |

| Panning                                      | 40 |

| To change the display region                 | 40 |

| To configure panning distance                | 40 |

| Moving to a location, reference, or bookmark | 40 |

| To move to a specific location               | 40 |

| To move a specific distance                  | 41 |

| To move to a specific grid reference         | 41 |

| To move to a specific bookmark               | 41 |

| Using Zoom                                   | 41 |

| Zooming In                                   | 41 |

| Zooming out                                  | 42 |

| Zooming to a specific scale                  | 42 |

| Changing the zoom factor                       | 43 |

|------------------------------------------------|----|

| Viewing the entire schematic page or part      | 43 |

| Viewing a specific area                        | 43 |

| Centering the view                             | 43 |

| Refreshing the display                         | 43 |

| Setting a bookmark                             | 44 |

| To place a bookmark                            | 44 |

| To rename a bookmark                           | 44 |

| Non-Linear Editor (Fisheye)                    | 44 |

| Fisheye view                                   | 45 |

| To switch to the Fisheye mode                  | 45 |

| Fisheye focus                                  | 45 |

| To Set the Fisheye focus                       | 45 |

| To Remove the Fisheye focus                    | 45 |

| Fisheye Dynamic Focus Mode                     | 45 |

| Non-Linear Zoom                                | 45 |

| To zoom in (non-linear)                        | 46 |

| To zoom out (non-linear)                       | 46 |

| Manipulating Objects in the Editors            | 46 |

| Moving objects                                 | 46 |

| Copying objects                                | 47 |

| Rotating objects                               | 48 |

| Mirroring objects                              | 48 |

| Selecting and deselecting objects              | 48 |

| Working with Text and Graphics                 | 50 |

| Creating graphics                              | 50 |

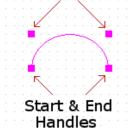

| Drawing Arcs                                   | 51 |

| Drawing Bezier Curves                          | 52 |

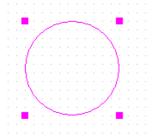

| Drawing Ellipses and Circles                   | 53 |

| Drawing Elliptical Arcs                        | 54 |

| Drawing lines                                  | 55 |

| Drawing polylines                              | 55 |

| Drawing Rectangles and Squares                 | 56 |

| Placing IEEE symbols                           | 56 |

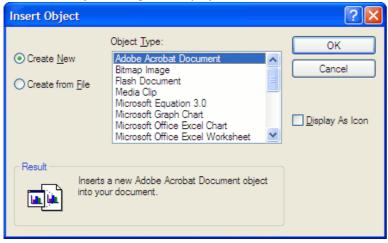

| Placing OLE Objects                            | 57 |

| Placing Pictures                               | 58 |

| Placing Text                                   | 59 |

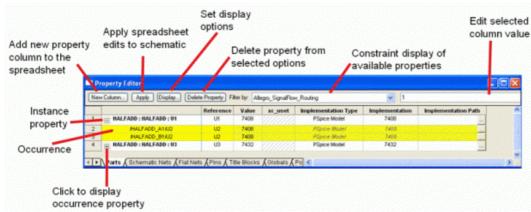

| The Property Editor                            | 59 |

| The Property editor window                     |    |

| Changing the appearance of the property editor |    |

| Using the Filters menu in the property editor  |    |

| Property Edit menu options                     |    |

| Show                                           | 65 |

| Hide                                           | 65 |

| Optional                                       | 65 |

| Undefined                                                                              | 66 |

|----------------------------------------------------------------------------------------|----|

| Show Undefined                                                                         | 66 |

| Invert Filter                                                                          | 66 |

| Add Filter                                                                             | 66 |

| Remove Current Filter                                                                  | 66 |

| Use the Property Editor Filter                                                         | 66 |

| Create a New Filter in the Property Editor                                             | 66 |

| Edit a Filter                                                                          | 67 |

| Using the Spreadsheet Editor                                                           | 67 |

| The property editor                                                                    | 67 |

| The Browse spreadsheet editor                                                          | 67 |

| To create a new property in the Browse spreadsheet editor                              | 68 |

| To copy a value from one property to another property in the Browse spreadsheet editor | 68 |

| To remove a user-defined property in the Browse spreadsheet editor                     | 69 |

| To replace property values                                                             | 69 |

| The Package Properties spreadsheet editor                                              | 69 |

| Update                                                                                 | 70 |

| Validate                                                                               | 70 |

| Capture Toolbars                                                                       | 70 |

| Capture toolbar                                                                        | 70 |

| CIS Explorer toolbar                                                                   | 70 |

| Part Manager toolbar                                                                   | 70 |

| Footprint Viewer toolbar                                                               | 70 |

| Pspice toolbar                                                                         | 70 |

| FPGA toolbar                                                                           | 70 |

| Search toolbar                                                                         | 70 |

| Draw toolbar                                                                           | 70 |

| Analyze toolbar                                                                        | 71 |

| Customizing toolbars                                                                   | 71 |

| Docking Toolbars                                                                       | 71 |

| To move a toolbar                                                                      | 71 |

| To hide a toolbar                                                                      | 71 |

| Working with multiple windows                                                          | 71 |

| To open a window on the active document                                                | 72 |

| To open a window on another document                                                   | 72 |

| To switch to a different open window                                                   | 72 |

| To switch to the project manager for the active document                               | 72 |

| To save all open windows                                                               | 72 |

| To close all open windows                                                              | 73 |

| To close all open tabs                                                                 | 73 |

| To close all open tabs except one                                                      | 73 |

| Setting the Window State                                                               | 73 |

| Searching in Capture                                                                   | 74 |

| To locate an object in a project                                                       | 74 |

| Searching a Design Hierarchy                                                           | 75 |

| Design Level                                                   | 75 |

|----------------------------------------------------------------|----|

| Folder Level:                                                  | 75 |

| Page Level:                                                    | 75 |

| Multiple Object selection.                                     | 75 |

| Find Toolbar                                                   | 75 |

| Find Window Search Results                                     | 76 |

| Edit Properties                                                | 76 |

| Save as HTML                                                   | 77 |

| Save as CSV                                                    | 77 |

| Session Log Search Results                                     | 77 |

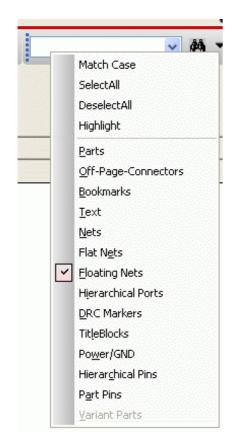

| Browsing in Capture                                            | 78 |

| To browse a design                                             | 78 |

| To display a list of parts in a library                        | 78 |

| To display a list of parts in the design cache                 | 79 |

| To list all objects of one type                                | 79 |

| To limit the list of objects                                   | 79 |

| Capture configuration                                          | 79 |

| Capture User Interface                                         | 79 |

| Capture.ini File                                               | 80 |

| Location of Capture.ini                                        | 80 |

| Capture ini Variables                                          | 81 |

| Re-initializing Capture.ini                                    | 81 |

| Capture CIS Settings                                           | 81 |

| Customizing Menus and Toolbars                                 | 81 |

| 3.                                                             | 83 |

| Working with Projects                                          | 83 |

| Creating a Project                                             | 83 |

| Project types                                                  | 83 |

| To create a project with the project wizard                    | 84 |

| Changing the Project type                                      | 85 |

| Setting Project Preferences                                    | 86 |

| Setting colors for objects on the schematic page               | 86 |

| Controlling the grid display                                   | 87 |

| To control the grid                                            | 87 |

| Customizing placement and movement of objects on the schematic | 87 |

| To specify grid style, spacing and visibility                  | 89 |

| To change snap to grid                                         | 90 |

| Setting pan and zoom                                           | 90 |

| Pan                                                            | 90 |

| Zoom                                                           | 90 |

| To configure zoom factor and auto scroll percent               | 90 |

| Defining selection options                                     | 90 |

| To define selection options                                    | 91 |

| Setting miscellaneous options                                  | 91 |

| Fill Style                                                     | 91 |

| Line Style and Width                                                      | 92  |

|---------------------------------------------------------------------------|-----|

| Color                                                                     | 92  |

| Project Manager and Session Log                                           | 92  |

| Enable inter-tool communication                                           | 92  |

| Text Rendering                                                            | 92  |

| Auto Recovery                                                             | 92  |

| To set miscellaneous options                                              | 93  |

| Setting Text editor options                                               | 94  |

| Setting up the Design Template                                            | 94  |

| Defining fonts for new designs                                            | 95  |

| To assign fonts for new designs                                           | 95  |

| Defining the title block                                                  | 95  |

| Default title block                                                       | 95  |

| To choose a title block and define the text it contains                   | 98  |

| To edit title block information                                           | 98  |

| To edit title block information on multiple pages                         | 98  |

| To change the display of title block information                          | 99  |

| Shortcuts                                                                 | 99  |

| Setting up a page                                                         | 99  |

| To set up the schematic page size                                         | 99  |

| Defining the grid reference                                               | 100 |

| To define the grid reference                                              | 100 |

| Specifying the default hierarchy option for new projects                  | 100 |

| To define the default hierarchy option                                    | 101 |

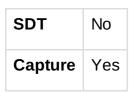

| Setting compatibility with OrCAD Schematic Design Tools                   | 101 |

| To set up compatibility with OrCAD Schematic Design Tools                 | 104 |

| Changing the SDT compatibility options for a single design                | 104 |

| Translating part fields from SDT to Capture properties                    | 105 |

| Translating Capture properties to SDT part fields                         | 105 |

| Dragging and dropping Folders, Pages, and Parts                           | 105 |

| Capture Directory Map                                                     | 106 |

| Capture directory contents                                                |     |

| Capture file types                                                        | 107 |

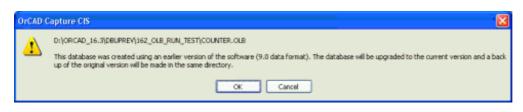

| Opening a project                                                         |     |

| To open an existing project                                               |     |

| To open a recently used project                                           |     |

| Saving a project, design, or library                                      | 109 |

| To save a new design or library                                           | 110 |

| To save an existing project                                               | 110 |

| To save one project                                                       | 110 |

| To save a project file along with the design file to a different location | 111 |

| To save one schematic page                                                |     |

| To save one design                                                        | 111 |

| Closing a Project                                                         | 112 |

| To close a project:                                                       | 112 |

| 4.                                                                      | 113 |

|-------------------------------------------------------------------------|-----|

| Working with Designs                                                    | 113 |

| Creating a Design                                                       | 114 |

| During Project Creation                                                 | 114 |

| Outside a Project                                                       | 114 |

| To create a Design                                                      | 114 |

| Working with Title Blocks                                               | 115 |

| Setting up the default title block                                      | 117 |

| To specify information for title block fields                           | 118 |

| To select a default title block symbol                                  | 118 |

| To create fields that are automatically filled on a default title block | 118 |

| Creating a custom title block                                           | 119 |

| To create a custom title block symbol                                   | 119 |

| To provide information for the fields of a custom default title block   | 120 |

| Placing Multiple Title Blocks                                           | 120 |

| To place custom title blocks                                            | 120 |

| Opening a Design                                                        | 120 |

| To open an existing design                                              | 120 |

| To open a recently used project                                         | 121 |

| Creating a new VHDL or Verilog file                                     | 121 |

| To create a new VHDL or Verilog file                                    | 121 |

| Creating a Text File                                                    | 122 |

| To create a text file from the Project manager                          | 122 |

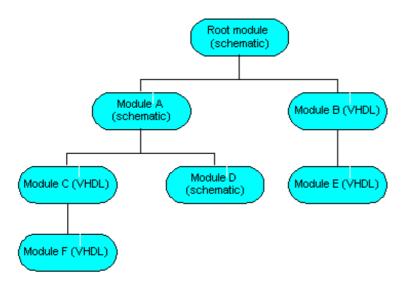

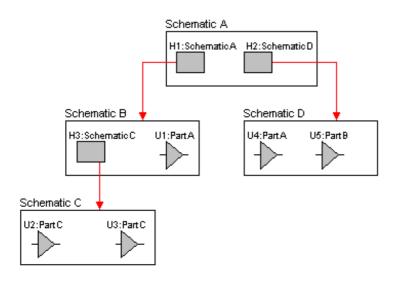

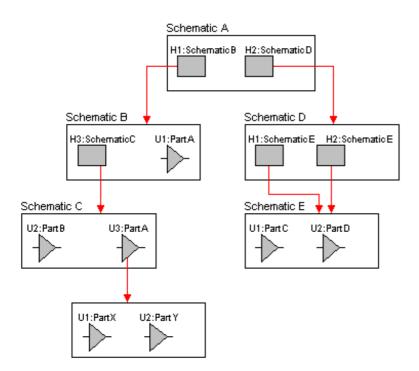

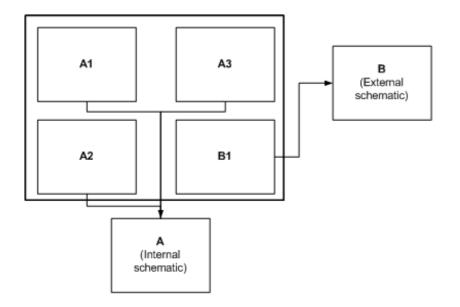

| Flat vs. hierarchical designs                                           | 122 |

| Flat designs                                                            | 122 |

| Hierarchical designs                                                    | 122 |

| Simple hierarchies                                                      | 123 |

| Complex hierarchies                                                     | 123 |

| Editing Hierarchical block look and feel                                | 124 |

| To place a graphical object on a hierarchical block                     | 124 |

| To change the look and feel of a hierarchical block                     | 124 |

| Renaming a Design                                                       | 125 |

| To rename a design                                                      | 125 |

| Saving and Closing a Design                                             | 125 |

| To save a design                                                        | 125 |

| To save a design to a different location                                | 125 |

| To close a design                                                       | 126 |

| 5.                                                                      | 127 |

| Working with Schematic Folders                                          | 127 |

| Creating a Schematic Folder                                             | 127 |

| Deleting a Schematic Folder                                             | 127 |

| Renaming a Schematic Folder                                             | 128 |

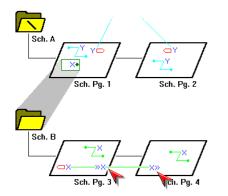

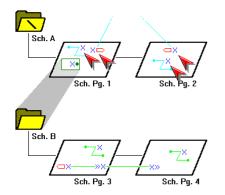

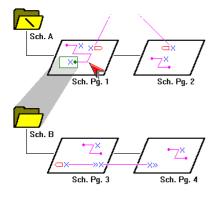

| Moving Schematic Folders                                                | 128 |

| Attaching a Schematic Folder                                            | 129 |

| Recommendations on Attaching a Schematic Folder        | 131 |

|--------------------------------------------------------|-----|

| 6.                                                     | 133 |

| Working with Schematic Pages                           | 133 |

| Creating a Schematic Page                              | 133 |

| Defining Schematic Page Characteristics                | 133 |

| Working with Label States                              | 135 |

| Working with VHDL and Verilog files                    | 136 |

| Creating a VHDL Model from a Hierarchical Block        | 136 |

| Creating a Verilog Model from a Hierarchical Block     | 138 |

| Checking the syntax of VHDL or Verilog files           | 140 |

| Moving Schematic Pages                                 | 140 |

| Renaming a Schematic Page                              | 143 |

| Deleting a Schematic Page                              | 143 |

| Closing and Saving a Schematic Page                    | 144 |

| 7.                                                     | 145 |

| Working with Part Libraries                            | 145 |

| Adding a Library to your Project                       | 145 |

| Creating a Library                                     | 146 |

| Opening a Library                                      | 147 |

| Editing a Library                                      | 148 |

| Copying a Part from the Design Cache to a Library      | 148 |

| Copying a Schematic Page to a Library                  | 148 |

| Copying a Schematic Folder to or from a Library        | 149 |

| Moving Parts or Symbols between Libraries              | 151 |

| Renaming a Library                                     | 152 |

| To rename a library:                                   | 152 |

| Closing and Saving a Library                           | 152 |

| Using the Library Correction Utility                   | 153 |

| Library Correction Utility                             | 153 |

| Starting the Library Correction Utility                | 153 |

| Verifying/Correcting Library Components With           | 153 |

| Missing Pin Numbers                                    | 153 |

| Missing pins Log File Example:                         | 153 |

| Duplicate Pin Names                                    | 154 |

| Verifying vs. Correcting                               | 155 |

| Changing ??Casing of Pin Names and Numbers             | 155 |

| Making Power Pins Visible                              | 156 |

| Advantages of this Utility in the Flow                 | 156 |

| Use Model for Capture-PCB Editor Flow                  | 156 |

| For New Designs:                                       | 156 |

| Correcting Existing Designs:                           | 156 |

| What if you do not have libraries for Existing Design? | 156 |

| Assumption:                                            | 156 |

| Known Limitation:                                      | 157 |

| 8.                                                      | 158 |

|---------------------------------------------------------|-----|

| Working with Parts                                      | 158 |

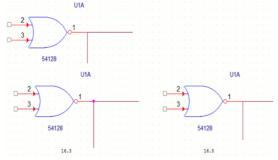

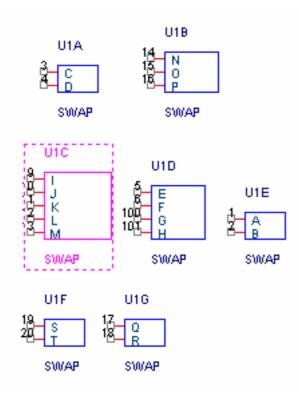

| Heterogeneous and Homogeneous Parts                     | 158 |

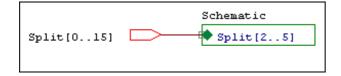

| Split parts                                             | 159 |

| Type of Packages                                        | 160 |

| Placing Parts on a Schematic Page                       | 160 |

| Searching for a Part                                    | 160 |

| Placing a Part                                          | 162 |

| Creating hierarchical blocks                            | 164 |

| Attaching a schematic folder to a hierarchical block    | 164 |

| Creating a hierarchical block from a Verilog model      | 166 |

| Creating a hierarchical block from a VHDL model         | 167 |

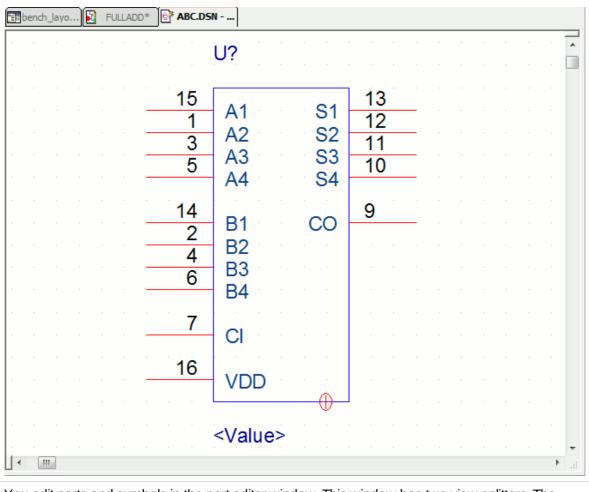

| Creating Parts                                          | 167 |

| Creating a Part Body                                    | 168 |

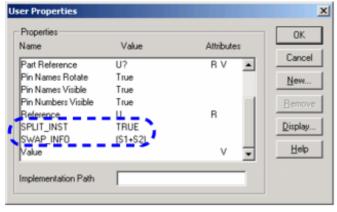

| Pin Shapes                                              | 174 |

| Creating a Part Convert                                 | 178 |

| Creating a Part Alias                                   | 178 |

| Creating a Part from a Spreadsheet                      | 179 |

| To add a pin                                            | 181 |

| To delete a pin                                         | 181 |

| Editing and Renaming a Part                             | 182 |

| Part Properties                                         | 183 |

| Assigning Properties to a Part                          | 184 |

| Renaming and deleting part properties                   | 188 |

| Update Properties using an Update File                  | 188 |

| Replacing and Updating the cache                        | 189 |

| Part Packages                                           | 191 |

| Creating a Package                                      | 191 |

| Creating a package                                      | 191 |

| Editing, Deleting, and Viewing a Package                | 194 |

| Viewing a Package                                       | 196 |

| To view all parts in a package                          |     |

| To switch to a different part in the package            |     |

| Synchronizing parts                                     |     |

| Part Instances and Occurrences                          |     |

| Removing part reference assignments                     |     |

| Generating library parts                                |     |

| Generating a part from a PSpice model library           |     |

| Creating a split part                                   | 201 |

| Adding pins to Split Part Section Input Spreadsheet     | 204 |

| Deleting pins from Split Part Section Input Spreadsheet | 204 |

| Viewing split part properties                           |     |

| Viewing split part package and its properties           | 205 |

| Deleting a Part                                         | 206 |

| 9.                                                      | 207 |

| Working with Properties                                                 | 207 |

|-------------------------------------------------------------------------|-----|

| Push Occurrence Properties into Instance Utility                        | 208 |

| Defining properties                                                     | 212 |

| Editing properties                                                      | 213 |

| Importing part and pin properties                                       | 215 |

| Exporting part and pin properties                                       | 216 |

| For libraries                                                           | 221 |

| 10.                                                                     | 223 |

| Managing Projects                                                       | 223 |

| Archiving a Project                                                     | 223 |

| Auto Recovery                                                           | 227 |

| Auto-Saving files                                                       | 228 |

| Adding and Deleting Project files                                       | 229 |

| Adding files to a Project                                               | 229 |

| Deleting Files from a Project                                           | 229 |

| Undoing and Repeating commands                                          | 230 |

| T o undo an action                                                      | 232 |

| Graphical Operation (GOp) Locking                                       | 233 |

| Locking and Unlocking Objects in a Design                               | 233 |

| Features of a Locked Schematic Page object                              | 234 |

| Features of a Locked Schematic Page                                     | 235 |

| Features of a Locked Schematic Folder                                   | 235 |

| Features of a Locked Design                                             | 236 |

| Cascading and Roll-up effects of Locking                                | 236 |

| 11.                                                                     | 238 |

| Establishing connectivity                                               | 238 |

| Wire connectivity                                                       | 238 |

| In this section:                                                        | 238 |

| Placing and naming wires                                                | 239 |

| To place a wire                                                         | 239 |

| To place a non-orthogonal w ire                                         | 239 |

| To attach a wire to a net                                               | 239 |

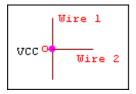

| Placing junctions                                                       | 240 |

| To create a junction while placing a wire                               | 240 |

| To place a junction on existing wires                                   | 240 |

| To select a junction                                                    | 240 |

| To remove a junction                                                    | 240 |

| Junction Dot Formation                                                  | 241 |

| Junction on straight wire-break only                                    | 241 |

| Junction Dot Formation v16.5 and prior releases                         | 241 |

| Auto-Wiring in Capture                                                  | 242 |

| Auto-Wire two points                                                    | 242 |

| To wire two points on a page (pin-to-pin, pin-to-wire or wire-to-wire). | 242 |

| Auto-Wire Multiple Points                                               | 243 |

| To auto-wire multiple points on a page                                     | 243 |

|----------------------------------------------------------------------------|-----|

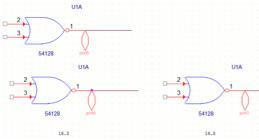

| Auto-Wire to Bus                                                           | 243 |

| To connect Part Pins and / or wires to a Bus                               | 243 |

| Auto-Wire to NetGroup                                                      | 244 |

| To auto-connect Part Pins and / or wires to a NetGroup wire                | 244 |

| To auto-connect Part Pins and / or wire to the signals in a NetGroup block | 244 |

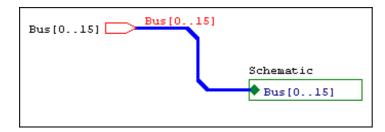

| Bus connectivity                                                           | 245 |

| As you place buses and wires:                                              | 246 |

| To create a bus                                                            | 246 |

| To place a non-orthogonal b us                                             | 246 |

| To name a bus                                                              | 246 |

| To connect single-signal nets to a bus                                     | 246 |

| Naming Conventions                                                         | 247 |

| For a Bus                                                                  | 247 |

| For a Bus Member                                                           | 247 |

| Modifying Wires and Buses                                                  | 247 |

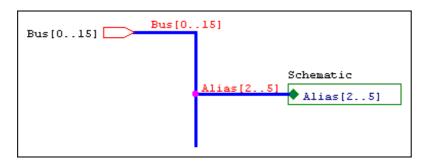

| Labeling wires and buses                                                   | 247 |

| To place an alias                                                          | 247 |

| To label a series of bus members                                           | 247 |

| Shortcut                                                                   | 247 |

| To edit net alias text                                                     | 247 |

| To move net alias text                                                     | 247 |

| Editing wire and bus look and feel                                         | 247 |

| To edit the look and feel of a wire or bus                                 | 248 |

| To edit the look and feel of a net                                         | 248 |

| Combining wire and net look and feel                                       | 248 |

| Scenario 1                                                                 | 248 |

| Scenario 2                                                                 | 248 |

| Moving Connectivity Objects                                                | 248 |

| Connectivity and orthogonal drag                                           | 248 |

| To drag a segment orthogonally                                             | 249 |

| To drag a segment non-orthogonally                                         | 249 |

| To move a wire or bus                                                      | 250 |

| To copy a wire                                                             | 250 |

| To move a vertex                                                           | 250 |

| Deleting wires and buses                                                   | 250 |

| To delete a wire or bus segment                                            | 250 |

| To delete a net                                                            | 250 |

| Shorting Part Pins                                                         | 250 |

| To short pins on a part                                                    | 250 |

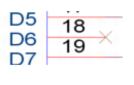

| Placing power, ground, and no connect symbols                              | 250 |

| No connect symbols                                                         | 250 |

| To place a no connect symbol                                               | 251 |

| To remove a no connect symbol                                              | 251 |

| Power and ground symbols                                                   | 251 |

| To place power or ground symbols                                                 | 251 |

|----------------------------------------------------------------------------------|-----|

| To rotate power or ground symbols                                                | 251 |

| To create a power or ground symbol                                               | 252 |

| To isolate a power net to a schematic folder                                     | 252 |

| To isolate a power net to a schematic page                                       | 252 |

| Working with Power Pins                                                          | 252 |

| Browsing for Power Pins                                                          | 252 |

| To browse the power pins in a design                                             | 252 |

| To change the properties of a power pin                                          | 252 |

| To change the power name of a pin                                                | 253 |

| Making power pins visible                                                        | 253 |

| To display invisible power pins                                                  | 253 |

| On a part instance                                                               | 253 |

| Throughout a design                                                              | 253 |

| To make power pins visible                                                       | 253 |

| On a new part                                                                    | 253 |

| On a part instance                                                               | 253 |

| Placing off-page connectors                                                      | 254 |

| To connect schematic pages laterally (within the schematic folder)               | 254 |

| To create a hierarchical port or off-page connector                              | 254 |

| Adding hierarchical ports                                                        | 254 |

| To connect pages vertically (through a hierarchical block)                       | 255 |

| To connect hierarchical ports or off-page connectors with nets                   | 256 |

| Establishing connectivity in schematic pages                                     | 256 |

| To extend a net across schematic pages within a single schematic folder          | 256 |

| To extend a net through a hierarchy                                              | 256 |

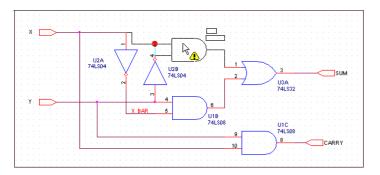

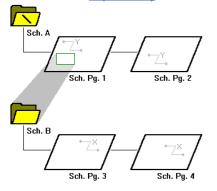

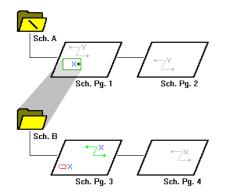

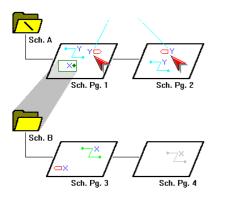

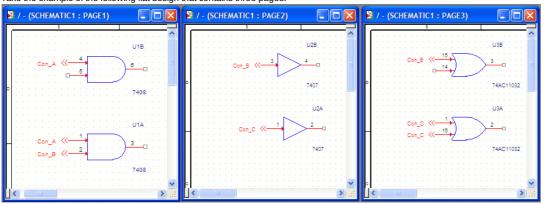

| EXAMPLE                                                                          | 257 |

| To establish the hierarchy with schematic folder??A "above" schematic folder??B: | 257 |

| To carry a net between schematic folders A and B:                                | 258 |

| Using intersheet references                                                      | 259 |

| Creating Intersheet references                                                   | 259 |

| To add intersheet reference s                                                    | 259 |

| To remove intersheet references                                                  | 260 |

| Guidelines for Creating Intersheet References                                    | 260 |

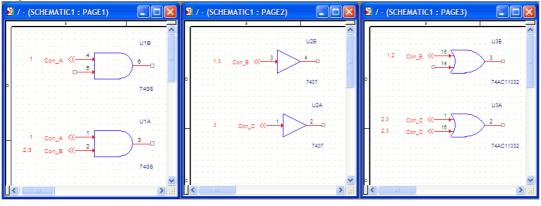

| Intersheet references in a flat design                                           | 261 |

| Con_A:                                                                           | 262 |

| Con_B                                                                            | 262 |

| Con_C                                                                            | 262 |

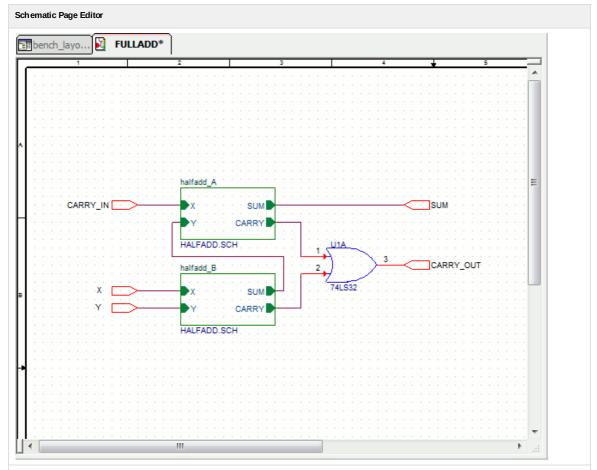

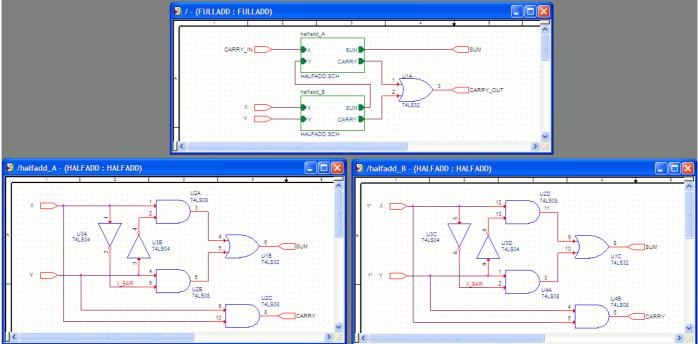

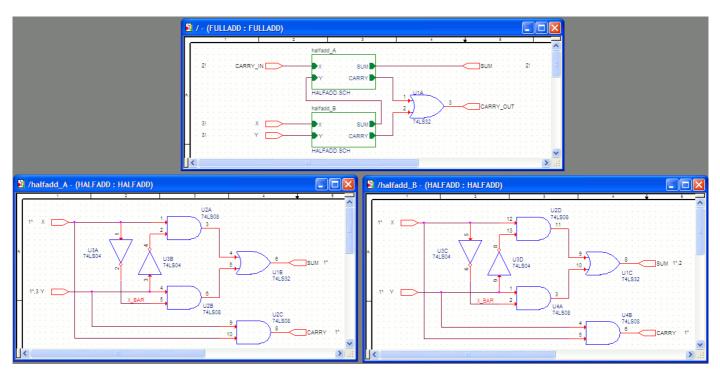

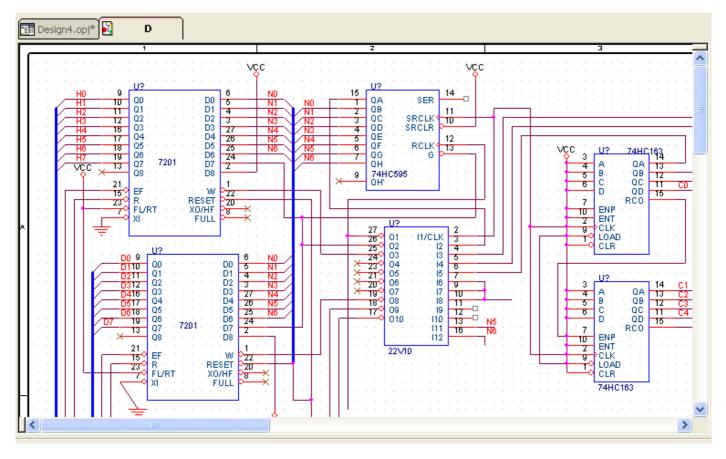

| Intersheet references in a hierarchical design                                   | 262 |

| CARRY_IN (FULLADD)                                                               | 263 |

| X (FULLADD)                                                                      | 263 |

| X (halfadd_A)                                                                    | 263 |

| Y (halfadd_A)                                                                    | 263 |

| Reporting Intersheet References                                                  | 263 |

| Signal Navigation in Capture                                                     | 264 |

| To find and navigate the signals on a design             | 264 |

|----------------------------------------------------------|-----|

| Working with nets                                        | 264 |

| Assigning net aliases                                    | 264 |

| To create a net alias                                    | 265 |

| To assign a net name                                     | 265 |

| To edit a net alias                                      | 265 |

| To move net alias text                                   | 265 |

| To display the net alias at multiple locations           | 265 |

| Net operations                                           | 265 |

| Find and Select a Net                                    | 266 |

| Edit Net Properties                                      | 266 |

| Delete a Net                                             | 266 |

| Tracing a net                                            | 266 |

| Find a Net Using a Name                                  | 266 |

| Locate and Highlight all Wires of a Net on a Single Page | 266 |

| Trace a Net Across Pages of a Schematic Folder           | 267 |

| To Trace a Net Between Schematic Folders                 | 267 |

| Using NetGroups                                          | 267 |

| Introducing NetGroups                                    | 268 |

| Named NetGroup                                           | 268 |

| To create a named NetGroup                               | 268 |

| To rename a NetGroup member                              | 270 |

| To modify a named associated NetGroup definition         | 270 |

| To delete a named NetGroup                               | 270 |

| Copy and paste NetGroups across designs                  | 270 |

| Exporting and Importing Associated NetGroup Definitions  | 270 |

| To export an Associated NetGroup to a Definition Xml     | 271 |

| To import an Associated NetGroup Definition Xml          | 271 |

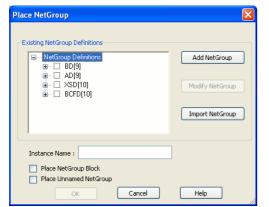

| Placing a named NetGroup on a page                       | 271 |

| To place a named NetGroup as a block                     | 271 |

| To place a named NetGroup as a hierarchical port         | 271 |

| To place a named NetGroup as an off-page connector       |     |

| To add or remove pins from a netgroup                    |     |

| To assign a NetGroup to a bus                            | 272 |

| Unnamed NetGroup                                         | 272 |

| To create an unnamed NetGroup                            |     |

| Placing an unnamed NetGroup as a block                   | 272 |

| Using the Place NetGroup dialog                          | 272 |

| Using the Schematic page edit pop-up menu                | 272 |

| To add a scalar member to an unnamed NetGroup            | 273 |

| To add a bus member to an unnamed NetGroup               | 273 |

| To delete a member from an unnamed NetGroup              | 273 |

| To place an unnamed NetGroup as a hierarchical port      | 273 |

| To place an unnamed NetGroup as an off-page connector    | 273 |

| To reorder pins in an unnamed NetGroup                   | 274 |

| NetGroup Reuse (Hierarchical Part Creation)                           | 274        |

|-----------------------------------------------------------------------|------------|

| To create a hierarchical part of a NetGroup                           | 274        |

| Components of a NetGroup Block                                        | 274        |

| NetGroup Entry/Exit Pin                                               | 274        |

| NetGroup Pin                                                          | 274        |

| NetGroup Wire                                                         | 274        |

| Netlising NetGroup Designs                                            | 274        |

| Other Netlists                                                        | 275        |

| NetGroup Connectivity                                                 | 275        |

| Named NetGroup Connectivity                                           | 275        |

| Using a Named NetGroup to connect signals across a hierarchy          | 275        |

| Using a Named NetGroup to connect signals across pages in a design    | 276        |

| Un-named NetGroup connectivity                                        | 277        |

| Using an Un-named NetGroup to connect signals across a hierarchy      | 277        |

| Using a Un-named NetGroup to connect signals across pages in a design | 277        |

| NetGroup and Bus Member Net Generation                                | 278        |

| Net Generation Scenarios                                              | 278        |

| 12.                                                                   | 283        |

| Automation in Capture                                                 | 283        |

| Working with Macros                                                   | 283        |

| Recording and Saving a Macro                                          | 283        |

| Recording a Macro                                                     | 283        |

| To record a macro                                                     | 283        |

| Saving a Macro                                                        | 284        |

| ······································                                | 284        |

| To save a configured macro<br>To add a macro                          | 285        |

| To remove macro                                                       | 285        |

| ······································                                | 285        |

| Playing a macro<br>To play the currently selected macro               | 285        |

| To play a macro                                                       | 285        |

|                                                                       | 286        |

| Macro input boxes<br>Creating macro shortcut keys                     | 280        |

| Macro Command Reference                                               | 280        |

| Selection commands                                                    | 287        |

| Macro Editing Commands                                                | 207        |

| Placement commands                                                    | 290        |

| PlaceArc                                                              | 292        |

| PlaceBlock                                                            | 293        |

| PlaceBookmark                                                         | 293        |

| ······································                                |            |

| PlaceBus<br>PlaceBusEntry                                             | 294        |

| PlaceBusEntry                                                         | 294        |

| PlaceEllipse<br>PlaceGround                                           | 294<br>204 |

| PlaceGround<br>PlaceJunction                                          | 294<br>205 |

|                                                                       | 295        |

| PlaceLine                                                             | 295        |

| PlaceNetAlias                                                        | 295 |

|----------------------------------------------------------------------|-----|

| PlaceNextPolygonPoint                                                | 295 |

| PlaceNextPolylinePoint                                               | 295 |

| PlaceNoConnect                                                       | 296 |

| PlaceOffPage                                                         | 296 |

| PlacePart                                                            | 296 |

| PlacePicture                                                         | 297 |

| PlacePin                                                             | 297 |

| PlacePolygon                                                         | 297 |

| PlacePolyline                                                        | 297 |

| PlacePort                                                            | 297 |

| PlacePower                                                           | 298 |

| PlaceRectangle                                                       | 298 |

| PlaceText                                                            | 298 |

| PlaceTitleblock                                                      | 298 |

| PlaceWire                                                            | 299 |

| Property commands                                                    | 299 |

| Viewing commands                                                     | 300 |

| Working with Capture TCL                                             | 302 |

| Using the Capture Command window                                     | 303 |

| To Open the Command window                                           | 303 |

| Registering and Logging TCL Commands                                 | 303 |

| Menu Commands                                                        | 303 |

| Page Editor Commands                                                 | 303 |

| Project Manager Commands                                             | 303 |

| Executing a TCL Command                                              | 304 |

| Creating a Capture TCL Script                                        | 304 |

| TCL Script for all Capture commands                                  | 304 |

| Location of the TCL file                                             | 305 |

| Capture Dialog settings in TCL                                       | 305 |

| TCL script for specific Capture commands                             | 305 |

| To create a script of a set of Capture commands                      |     |

| Executing a Capture TCL script                                       |     |

| Execute TCL script in Capture                                        | 306 |

| Execute TCL script in Windows                                        | 306 |

| 13.                                                                  | 307 |

| Processing the Design                                                | 307 |

| Annotating the Design                                                | 307 |

| Customizing Part References in a Design                              | 307 |

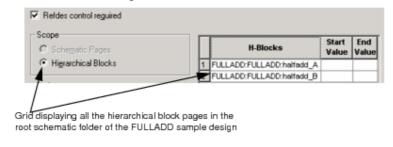

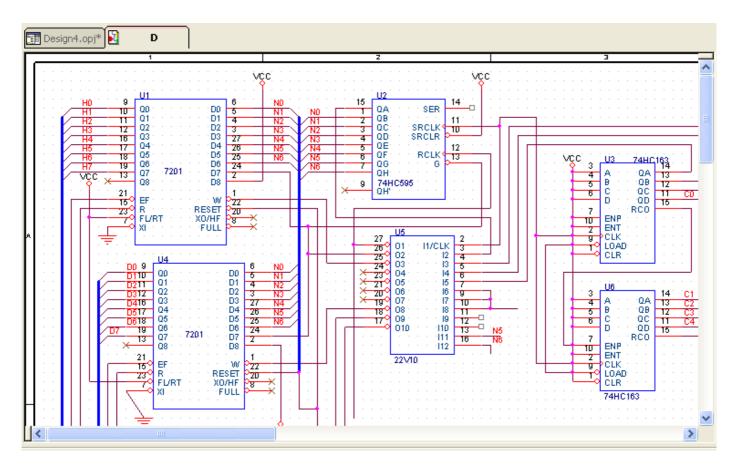

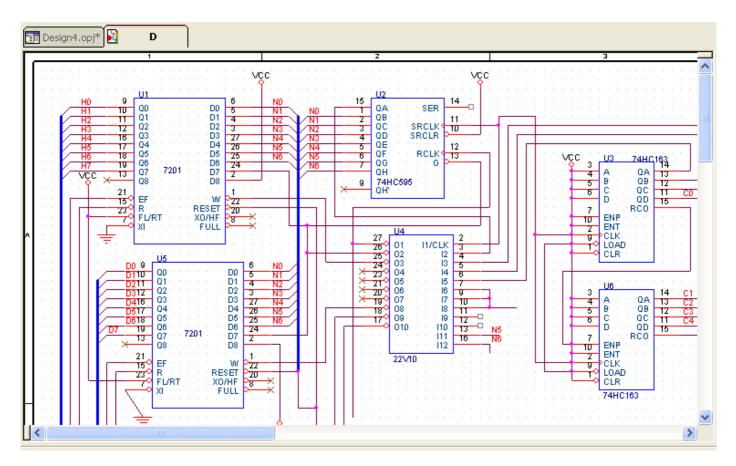

| Schematic page-wise and hierarchical block-wise annotation           | 308 |

| To perform schematic page-wise or hierarchical block-wise annotation | 308 |

| Back Annotating                                                      | 310 |

| Forward Annotating Schematic Information                             | 311 |

| Choosing the Annotate Sequence                                       | 311 |

| Designating Pins, Gates, or Packages for Swapping                    | 315 |

| Creating a swap file (.SWP)                      | 315 |

|--------------------------------------------------|-----|

| CHANGEREF                                        | 315 |

| GATESWAP                                         | 316 |

| PINSWAP                                          | 316 |

| CHANGEPIN                                        | 316 |

| Creating an update file                          | 317 |

| Creating a Combined Swap and Update File         | 319 |

| Example                                          | 320 |

| Generating Reports                               | 320 |

| Creating an Include File                         | 321 |

| Example                                          | 321 |

| Creating a Bill of Materials                     | 322 |

| Creating a Cross Reference Report                | 324 |

| Example                                          | 324 |

| Creating a Placement Report                      | 325 |

| Creating a Find Result Report                    | 325 |

| Check and Save                                   | 326 |

| Printing and plotting                            | 326 |

| Printer or Plotter Setup                         | 327 |

| Special considerations for plotters              | 327 |

| Plotter pen colors                               | 327 |

| Setting Print Options for Schematic Page Objects | 327 |

| Printing Documents                               | 328 |

| Printing or plotting a schematic page            | 329 |

| Previewing Print Output                          | 330 |

| Printing or Plotting a Part                      | 330 |

| Scaling a Print or Plot                          | 331 |

| Netlisting a Design                              | 331 |

| Net name resolution                              | 332 |

| Create Netlist dialog box tabs                   | 334 |

| Creating a Netlist                               | 335 |

| Creating a Flat Netlist                          | 335 |

| Working with Hierarchical Netlists               | 335 |

| In this section:                                 | 335 |

| Creating a Hierarchical Netlist                  | 336 |

| Customizing a Hierarchical Netlist               | 336 |

| Creating Subcircuit Netlists                     |     |

| Using SUBPARAM                                   | 338 |

| Example                                          | 338 |

| Specifying an Alternate Netlist Template         | 340 |

| 14.                                              | 341 |

| Simulating Capture Designs Using PSpice          | 341 |

| Overview of Simulation Using PSpice              | 2/1 |

| Creating Projects for Simulation                 | 342 |

| Creating a new project                           | 342 |

|                                                                                         | 0.40       |

|-----------------------------------------------------------------------------------------|------------|

| Setting up an existing project for simulation                                           | 343<br>343 |

| Preparing a Design for Simulation<br>Adding PSpice and parametrized libraries and parts | 343<br>344 |

| Special simulation-only parts                                                           | 344        |

|                                                                                         | 345        |

| Vendor-supplied parts                                                                   | 345<br>345 |

| Standard PSpice libraries                                                               |            |

| PSpice Advanced Analysis libraries                                                      | 345        |

| Part naming conventions                                                                 | 346        |

| Finding the part that you want                                                          | 346        |

| Passive parts                                                                           | 348        |

| Breakout parts                                                                          | 348        |

| Behavioral parts                                                                        | 349        |

| Analog behavioral parts                                                                 | 349        |

| Digital behavioral parts                                                                | 350        |

| Defining part properties needed for simulation                                          | 350        |

| Editing simulation properties                                                           | 350        |

| PSPICETEMPLATE property                                                                 | 351        |

| PSPICETEMPLATE syntax                                                                   | 351        |

| PSPICETEMPLATE examples                                                                 | 353        |

| IO_LEVEL property                                                                       | 355        |

| MNTYMXDLY property                                                                      | 355        |

| PSPICEDEFAULTNET property                                                               | 356        |

| Guidelines and best practices for specifying values for part properties                 | 356        |

| Placing PSpice Ground 0 Symbols for PSpice Simulations                                  | 357        |

| Using the FLOAT property for unconnected pins                                           | 357        |

| Using Global Parameters and Expressions                                                 | 358        |

| Global parameters                                                                       | 358        |

| Declaring and using a global parameter                                                  | 359        |

| Expressions                                                                             | 360        |

| Specifying expressions                                                                  | 360        |

| Associating PSpice model to a Capture symbol                                            | 361        |

| Importing PSpice Schematic Projects in Capture                                          | 364        |

| Defining Stimuli                                                                        | 364        |

| Analog stimuli                                                                          | 365        |

| Using VSTIM and ISTIM                                                                   | 365        |

| Using VSRC or ISRC parts                                                                | 366        |

| Digital stimuli                                                                         | 367        |

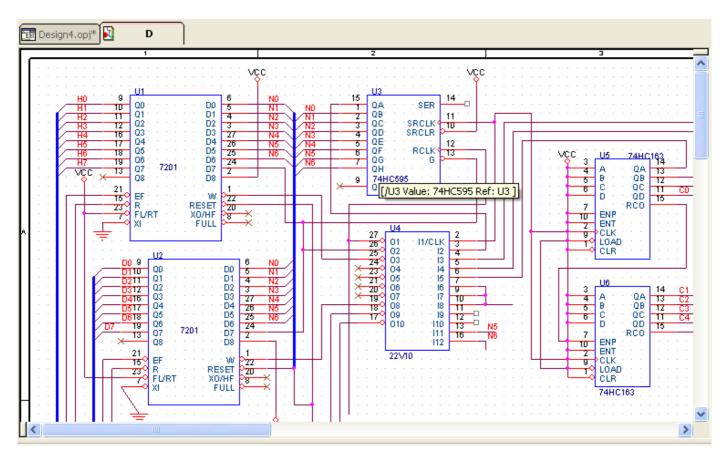

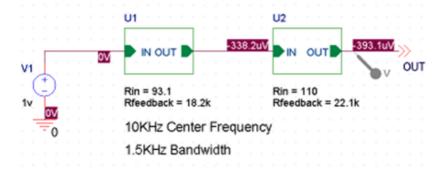

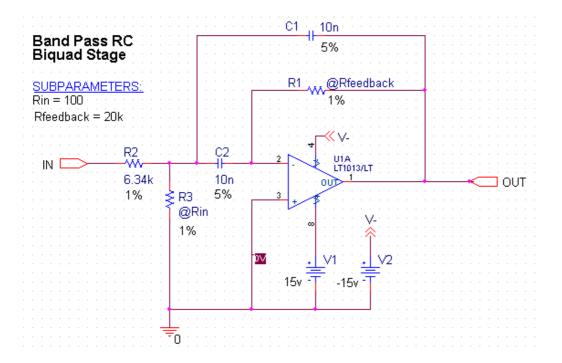

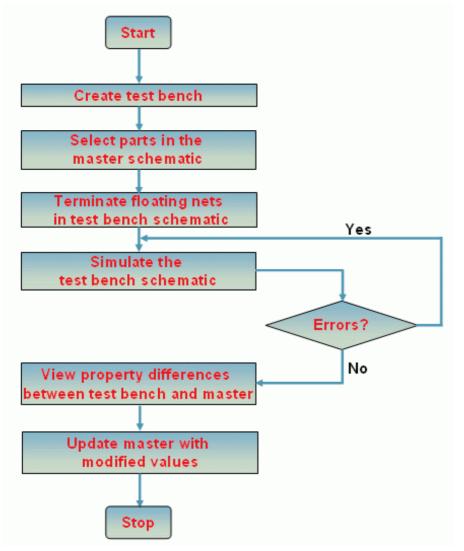

| Using Partial Design Simulation                                                         | 367        |

| Working with a Test Bench                                                               | 369        |

| Creating a Test Bench                                                                   | 369        |

| Activating Components                                                                   | 369        |

| Comparing and Updating Master Design                                                    | 371        |

| Running a Simulation and Viewing Results Using PSpice                                   | 372        |

| Creating a new simulation profile                                                       | 372        |

| Creating a simulation netlist                                                           | 373        |

| Viewing a simulation netlist                                  | 374 |

|---------------------------------------------------------------|-----|

| Running a simulation                                          | 374 |

| Viewing the results as the simulation progresses              | 375 |

| Viewing the most recent simulation results                    | 375 |

| Viewing the output file                                       | 375 |

| Editing simulation settings                                   | 375 |

| Placing markers                                               | 376 |

| Showing, hiding, and deleting markers                         | 376 |

| Simulating and viewing the results of multiple profiles       | 377 |

| Making a simulation profile active                            | 377 |

| Files Needed for Simulation                                   | 377 |

| Files that Design Entry Programs generate                     | 378 |

| Netlist file                                                  | 378 |

| Other files that you can configure for simulation             | 378 |

| Model library                                                 | 378 |

| Stimulus file                                                 | 379 |

| Include file                                                  | 379 |

| Configuring model library, stimulus, and include files        | 379 |

| Files that PSpice generates                                   | 380 |

| Probe data file                                               | 380 |

| PSpice output file                                            | 380 |

| Running PSpice in Batch Mode                                  | 381 |

| Interactive Mode                                              | 381 |

| Non-Interactive Mode                                          | 381 |

| SPICE netlist format                                          | 381 |

| 15.                                                           | 385 |

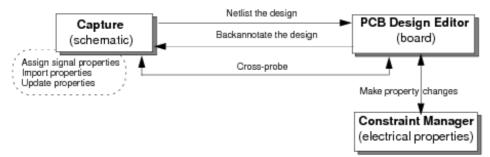

| Physical Layout in PCB Editor                                 | 385 |

| Preparing the Schematic for Layout                            | 385 |

| Best practices for Capture-PCB Editor flow                    | 386 |

| Unsupported Capture-PCB Flow field values                     | 387 |

| Assigning Physical Properties to a Schematic Design           | 387 |

| Methods to assign properties in Capture for use in PCB Editor | 387 |

| Assigning Footprint Properties                                | 388 |

| Why footprint?                                                | 388 |

| Locating Footprints in Install Hierarchy                      | 388 |

| Do all parts in my design have footprint information?         | 389 |

| Assigning footprints to components                            | 390 |

| Assigning Footprint to one component                          | 390 |

| Assigning same footprint to multiple components               | 391 |

| Specifying Alternate Footprints                               |     |

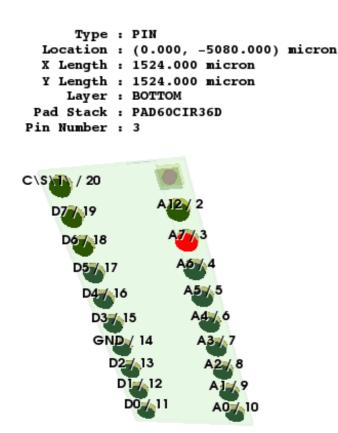

| Viewing Footprints in Capture                                 |     |

| 3D Footprint Viewer                                           | 392 |

| Footprint Views                                               | 392 |

| Moving the footprint                                          | 393 |

| Mapping symbol pins with footprint pins                       | 393 |

| Footprint Viewer Toolbar                                                       | 393 |

|--------------------------------------------------------------------------------|-----|

| Troubleshooting Footprint Viewing Errors                                       | 395 |

| Instance-Level Properties for Physical Design                                  | 396 |

| ROOM Property                                                                  | 396 |

| Defining Properties on Nets                                                    | 396 |

| Signal Property Flow                                                           | 397 |

| Limitations of the signal property flow                                        | 398 |

| PROPAGATION DELAY                                                              | 399 |

| RATSNEST SCHEDULE                                                              | 401 |

| RELATIVE PROPAGATION DELAY                                                     | 401 |

| DIFFERENTIAL PAIR                                                              | 404 |

| Creating Differential Pairs using Property Editor                              | 404 |

| Create Differential Pair Command                                               | 405 |

| To view a differential pair                                                    | 406 |

| To modify a differential pair                                                  | 406 |

| To delete a differential pair                                                  | 407 |

| Creating differential pairs between multiple pairs of flat nets simultaneously | 407 |

| To create multiple differential pairs simultaneously                           | 407 |

| The Voltage Property                                                           | 409 |

| Properties on Power Pins                                                       | 409 |

| POWER_PINS property                                                            | 409 |

| To use the POWER_PINS property                                                 | 409 |

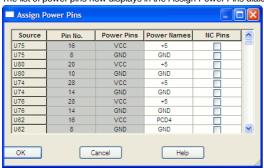

| Assigning Power Nets to Invisible Power Pins                                   | 410 |

| Using Assign Power Pins command                                                | 410 |

| Using the POWER_GROUP property                                                 | 412 |

| To avoid using visible power pins in the Capture-PCB Editor flow               | 412 |

| Reassigning power pin connections                                              | 413 |

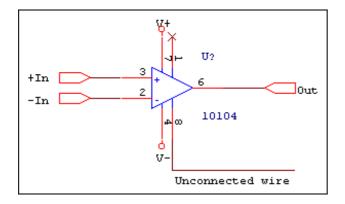

| Unconnected Pins in Capture-PCB Editor Flow                                    | 414 |

| Assigning "no connect" pins                                                    | 414 |

| Assigning "no connect" power pins                                              | 416 |

| To specify a power pin as an NC pin                                            | 416 |

| Property Flow from Capture to PCB Editor                                       | 417 |

| PCB Editor configuration file                                                  | 418 |

| How properties are netlisted from Capture to PCB Editor                        | 419 |

| User-Defined Properties in Capture - PCB Editor Flow                           | 420 |

| Guidelines for Updating Configuration File (allegro.cfg)                       | 421 |

| Aliasing properties in configuration file                                      | 421 |

| Generating PCB Editor Netlist                                                  | 422 |

| Generating Initial Board File                                                  | 424 |

| Cross Probing for PCB Editor                                                   | 425 |

| Cross selecting between Capture and Allegro PCB Editor                         | 426 |

| Cross highlighting between Capture and PCB Editor                              | 426 |

| Locking Components during Cross-Probing                                        | 427 |

| Pin Swapping In Capture-PCB Editor Flow                                        | 427 |

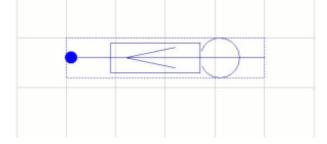

| Using the SWAP_INFO property                                                   | 428 |

| Using the SPLIT_INST property                                                   | 431        |

|---------------------------------------------------------------------------------|------------|

| NO_SWAP_COMP property                                                           | 432        |

| NO_SWAP_GATE property                                                           | 432        |

| NO_SWAP_GATE_EXT property                                                       | 432        |

| NO_SWAP_PIN property                                                            | 432        |

| Back Annotation from PCB Editor                                                 | 434        |

| Best practices for smooth back annotation                                       | 438        |

| Physical Layout of a Simulation Design                                          | 439        |

| Design Reuse for PCB Editor                                                     | 440        |

| Multi-level reuse designs                                                       | 441        |

| Creating a Reuse Design                                                         | 442        |

| To create a reuse design                                                        | 442        |

| Reuse properties                                                                | 443        |

| Using a Reuse Design                                                            | 445        |

| Reuse Module as a Library Part                                                  | 445        |

| Placement Guidelines                                                            | 445        |

| Reuse Module as Hierarchical Block                                              | 446        |

| Running Design Rules Check - Physical Rules                                     | 446        |

| Validating design for Physical Layout                                           | 446        |

| Browsing DRC markers                                                            | 447        |

| To browse DRC markers                                                           | 447        |

| Working with Old Designs                                                        | 448        |

| Moving from Capture-Layout Flow To Capture-PCB Editor Flow                      | 448<br>448 |

| Using the IGNORE_PROP property to ignore the DEVICE property on your design 16. | 440        |

|                                                                                 |            |

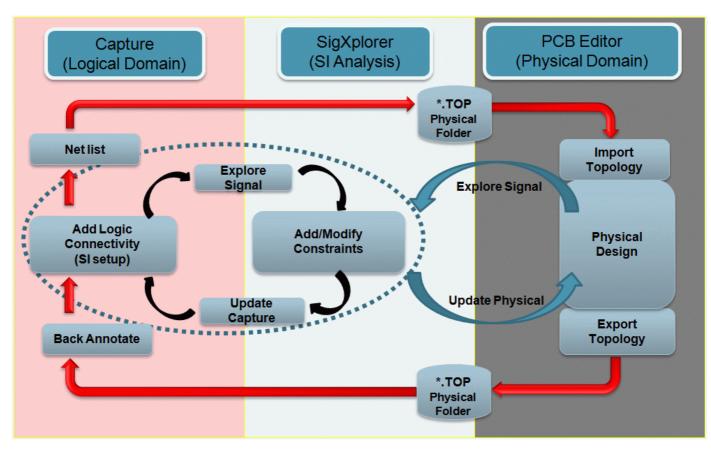

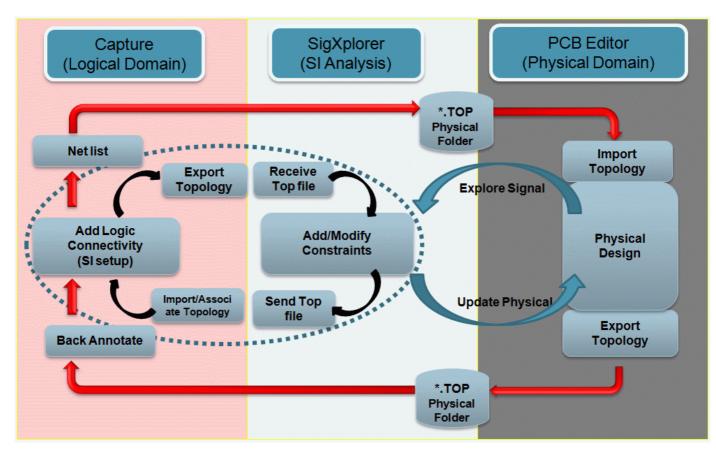

| Using Capture with PCB SI                                                       | 449        |

| Setting up a Library                                                            | 449        |

| Assigning Models                                                                | 450        |

| Managing Electrical Csets                                                       | 451        |

| Concurrent Mode                                                                 | 451        |

| Distributed Mode                                                                | 452        |

| Validating Electrical Csets                                                     | 453        |

| 17.                                                                             | 454        |

| Designing for FPGA                                                              | 454        |

| Overview of FPGA Projects                                                       | 454        |

| Creating a FPGA project                                                         | 455        |

| Compiling vendor simulation libraries                                           | 455        |

| Introducing NC VHDL simulations                                                 | 457        |

| Starting NC VHDL                                                                | 457        |

| Setting the Simulation Mode                                                     | 457        |

| Running NC VHDL in interactive mode                                             | 457        |

| Performing functional simulation                                                | 459        |

| Selecting the configuration for functional simulation                           | 459        |

| Performing Synthesis and Place-and-Route                                        | 460        |

| Synthesis with Synplify                                   | 460        |

|-----------------------------------------------------------|------------|

| Place-and-route using the vendor tool set                 | 461        |

| Performing Timing Simulation                              | 461        |

| Selecting the configuration for timing simulation         | 462        |

| Generating a part for FPGA projects                       | 462        |

| Overview of Part Generation for FPGA                      | 462        |

| Generating a part for your FPGA                           | 463        |

| Supported Vendor Pad and Pin file formats                 | 465        |

| Simulating the Board                                      | 466        |

| Choosing an HDL for board simulation                      | 466        |

| Starting NC VHDL or NC Verilog for board-level simulation | 466        |

| NC VHDL in Batch Mode                                     | 467        |

| VHDL and Verilog reserved words                           | 469        |

| VHDL reserved words                                       | 469        |

| Verilog reserved words                                    | 470        |

| 18.                                                       | 472        |

| PCB Editor netlist files                                  | 472        |

| PSTCHIP.DAT                                               | 472        |

| PSTCHIP File format                                       | 472        |

| PSTCHIP File Elements                                     | 473        |

| PSTCHIP Sample file                                       | 474        |

| PSTXNET.DAT                                               | 476        |

| PSTXNET File Elements                                     | 476        |

| PSTXNET File format                                       | 477        |

| PSTXNET Sample file                                       | 477        |

| PSTXPRT.DAT                                               | 481        |

| PSTXPRT File Elements PSTXPRT File format                 | 482        |

|                                                           | 483<br>484 |

| PSTXPRT Sample file                                       |            |

| 19.                                                       | 487        |

| SDT configuration files                                   | 487        |